# **Enhancing Side-channel Security:**

## Detection, Mitigation and Verification

### Ke Jiang

College of Computing and Data Science

A thesis submitted to the Nanyang Technological University in partial fulfillment of the requirements for the degree of Doctor of Philosophy

2024

$\bigodot$  2024 Ke Jiang

### Statement of Originality

I hereby certify that the work embodied in this thesis is the result of original research, is free of plagiarised materials, and has not been submitted for a higher degree to any other University or Institution.

06/10/2024

Date

Ke Jiang

### Supervisor Declaration Statement

I have reviewed the content and presentation style of this thesis and declare it is free of plagiarism and of sufficient grammatical clarity to be examined. To the best of my knowledge, the research and writing are those of the candidate except as acknowledged in the Author Attribution Statement. I confirm that the investigations were conducted in accord with the ethics policies and integrity standards of Nanyang Technological University and that the research data are presented honestly and without prejudice.

06/10/2024

Date

Giever

Assoc. Prof. Tianwei Zhang

### Authorship Attribution Statement

This thesis contains material from 2 papers accepted at conferences and 1 paper being reviewed by the conference in which I am listed as an author.

Chapter 2 is published as Ke Jiang, Yuyan Bao, Shuai Wang, Zhibo Liu, and Tianwei Zhang. 2022. Cache Refinement Type for Side-Channel Detection of Cryptographic Software. In Proceedings of the 2022 ACM SIGSAC Conference on Computer and Communications Security (CCS '22). Los Angeles, L.A., USA, 1583–1597. https://doi.org/10.1145/3548606.3560672

The contributions of the co-authors are as follows:

- I proposed the idea, developed the system and conducted all experiments.

- All data, including locating the vulnerabilities in cryptography libraries was analyzed by me.

- I prepared the manuscript drafts. The manuscript was revised by Asst/Prof Yuyan Bao, Assoc/Prof Shuai Wang and Assoc/Prof Tianwei Zhang.

- Asst/Prof Yuyan Bao assisted in the collation of the refinement type rules.

- Assoc/Prof Shuai Wang assisted with the rebuttal period and polished the revision.

- Dr. Zhibo Liu provided technical support on disassembly.

- Assoc/Prof Tianwei Zhang put forward constructive suggestions throughout the project.

Chapter 3 is being reviewed as Ke Jiang, Sen Deng, Yinshuai Li, Shuai Wang, Tianwei Zhang, and Yinqian Zhang. 2024. CipherGuard: Compiler-aided Mitigation against Ciphertext Side-channel Attacks.

The contributions of the co-authors are as follows:

- I proposed the idea, developed the system and conducted all experiments.

- I analyzed the data and wrote the draft of the manuscript. The draft was revised by Assoc/Prof Shuai Wang, Assoc/Prof Tianwei Zhang and Prof Yinqian Zhang.

- Sen Deng participated in the discussion of important project nodes and made valuable comments on the manuscript.

- Yinshuwai Li provided technical support on program debugging.

- Assoc/Prof Tianwei Zhang and Prof Yinqian Zhang guided the direction of the project.

- Assoc/Prof Shuai Wang put forward constructive suggestions throughout the project.

Chapter 4 is published as Ke Jiang, Tianwei Zhang, David Sanán, Yongwang Zhao, and Yang Liu. 2022. A Formal Methodology for Verifying Side-channel Vulnerabilities in Cache Architectures. In Proceedings of the 23rd International Conference on Formal Engineering Methods (ICFEM' 22), Madrid, Spain, 190-208. https://doi.org/10.1007/978-3-031-17244-1\_12

The contributions of the co-authors are as follows:

- I proposed the idea, developed the verification framework and conducted all proofs.

- I analyzed the proof results, specifically connecting the results to all cache designs. I prepared the manuscript.

- The manuscript was revised by Assoc/Prof Tianwei Zhang and Asst/Prof David Sanán.

- Assoc/Prof Tianwei Zhang and Prof Yongwang Zhao participated in the discussion of important project nodes.

- Asst/Prof David Sanán provided technical support on formal verification.

- Prof Yang Liu put forward constructive suggestions throughout the project.

06/10/2024

Date

Ke Jiang

### Acknowledgements

It is time to bid farewell to the Ph.D. journey, an unforgettable experience that has imparted invaluable lessons and fostered profound personal growth. The challenges and triumphs encountered along the way have not only deepened my knowledge and honed my research skills but also strengthened my resilience and broadened my perspective.

I would like to express my gratitude to my supervisor, Associate Professor Tianwei Zhang, for providing me the opportunity to pursue a Ph.D., as well as for offering valuable guidance in establishing the overall research direction. His mentorship fostered my capacity for independent scientific research and cultivated a nuanced approach to critical thinking. By granting me the freedom to explore and discover my research interests, he encouraged a spirit of inquiry and innovation, while consistently providing clear guidance and substantial help whenever needed. His exemplary conduct elucidated the qualities of a seasoned scientist, shaping my understanding of the caliber and demeanor expected in the pursuit of scholarly endeavors. His strict requirements and high standards challenged me to strive for excellence and significantly enhanced the quality of my work. For all these reasons, I am deeply thankful for his support and mentorship throughout my Ph.D. journey.

I express profound gratitude to Professor Yang Liu and Professor Yongwang Zhao for ushering me into the realm of academic pursuit during a transformative trip to Singapore. This marked the inception of my doctoral journey, altering the trajectory of my life significantly. Witnessing their dedication and exploration at the forefront of scientific frontiers served as a compelling inspiration. Their commitment to conducting research with calmness and rigor became a guiding beacon for me.

I would like to acknowledge Professor Yinqian Zhang, Associate Professor Shuai Wang, Assistant Professor David Sanán, and Assistant Professor Yuyan Bao, for

their collaborative efforts, which have contributed to the successful completion of various aspects of my doctoral journey. Their dedication and expertise have been indispensable, and I am grateful for the shared intellectual journey.

A heartfelt thank you to my friends, Kangjie Chen, Shuxin Li, Xiaoxuan Lou, Tianlin Li, Chengwei Liu, Meng Hao, Hanxiao Chen, Anran Li, Wenjun Long, Dr. Wenhao Fu, Gelei Deng, Dr. Jianwen Sun, Dr. Hongxu Chen, Dr. Fei Yang, Dr. Feng Zhang, Jinyi Xian and others who have provided emotional support, encouragement, and moments of respite during the challenging phases of this journey.

To my wife, my parents, and other family members, I am deeply indebted for their unwavering love, encouragement, and understanding throughout this journey. Their belief in my abilities have been a constant source of motivation. Their collective support has not only fortified my academic endeavors but has also been the bedrock of my personal growth. I am profoundly grateful for the invaluable contributions of my family, without whom this journey would not have been possible. Lastly, I am overjoyed to share that my wife has bestowed upon me the most precious gift of all, our daughter. Her arrival has filled our lives with immeasurable happiness and has added a new, profound dimension to our journey as a family. To my dear family

## Abstract

In the realm of computer security, side-channel attacks pose a significant threat by exploiting subtle information leaks during the operation of a system. These attacks, which include cache side-channel attacks, a particularly insidious subset, enable adversaries to extract sensitive data by exploiting cache memory behaviors. To defeat cache side-channel attacks, current research has made strides in developing software and hardware-level countermeasures, but challenges persist in achieving comprehensive and scalable methods. Furthermore, constant-time coding practices, effective against traditional cache-based side channels, face limitations with emerging threats like ciphertext side channels. Additionally, new micro-architectural designs, e.g., cache designs, lack formal guarantees of effectiveness, highlighting the need for ongoing evaluation and adaptability. This thesis addresses these challenges, with the aim of improving cache side-channel defense methods, addressing emerging ciphertext side channels, and improving the security of novel hardware designs through formal verification.

To be more specific, this thesis focuses on three primary objectives. First, it aims to advance cache side-channel detection by developing comprehensive methods to identify and mitigate vulnerabilities in cryptography software. Second, it addresses the emerging threat of ciphertext side channels by proposing a holistic approach that combines constant-time coding practices with compiler-aided mitigation mechanisms. Finally, the research seeks to enhance the security of new cache designs by providing a means for formal verification, acknowledging the challenges posed by their complexity and potential vulnerabilities. Through these endeavors, this thesis contributes to fortifying the security of modern computing systems against the evolving and increasingly sophisticated landscape of side-channel threats.

We present three significant contributions addressing side-channel vulnerabilities. Firstly, we introduce CATYPE, a groundbreaking refinement type-based tool for cache side-channel detection in cryptographic software. CATYPE analyzes x86 assembly code using refinement types, offering enhancements like bit-level granularity tracking, precise type inferences, and high scalability. It is the first static analyzer for cryptography libraries considering blinding-based defenses and utilizes cache layouts to suppress false positives, demonstrating superior performance in identifying vulnerabilities. Secondly, we propose CIPHERGUARD, a compiler-aided mitigation tool addressing ciphertext side channels by recognizing secret-dependent store instructions and providing multiple strategies to protect these instructions. For the first time, CIPHERGUARD employs various precise and flexible mitigation variants based on the LLVM ecosystem, achieving security without hardware modification and displaying enhanced efficiency in cryptography implementations compared to existing defense tools. Lastly, we introduce a formal methodology for security verification of cache architectures, employing an entropy-based noninterference reasoning framework to assess information leakage. The methodology, applied to eight cache architectures, demonstrates reliability and flexibility, contributing to the advancement of cache side-channel security.

# Contents

| Α  | ckno   | ledgements                                           |   |    |   |           | vii |

|----|--------|------------------------------------------------------|---|----|---|-----------|-----|

| A  | bstra  | et                                                   |   |    |   |           | xi  |

| Li | ist of | Figures                                              |   |    |   | x         | vii |

| Li | ist of | Tables                                               |   |    |   | 2         | xix |

| Sy | ymbc   | s and Acronyms                                       |   |    |   | 2         | xxi |

| 1  | Intr   | oduction                                             |   |    |   |           | 1   |

|    | 1.1    | Side-channel Attacks                                 |   |    |   |           | 1   |

|    |        | 1.1.1 Micro-architectural Side-channels              |   |    |   |           | 2   |

|    |        | 1.1.2 Trusted Computing Side-channels                |   |    |   |           | 3   |

|    |        | 1.1.3 Physical Side-channels                         |   |    |   |           | 4   |

|    | 1.2    | Side-channel Mitigation                              |   |    |   |           | 6   |

|    |        | 1.2.1 Secure Architectures and System Designs        |   |    |   |           | 6   |

|    |        | 1.2.2 Trusted Computing Hardening                    |   |    |   |           | 8   |

|    |        | 1.2.3 Constant-time Principles                       |   |    |   |           | 8   |

|    | 1.3    | Research Scope and Overview                          |   |    |   |           | 11  |

|    | 1.4    | Major Contributions                                  |   |    |   |           | 13  |

|    | 1.5    | Outline of the Thesis                                |   |    |   |           | 15  |

| 2  |        | nement type-based Detection of Side-channels in Cryp | t | эg | ŗ | <b>a-</b> |     |

|    |        | Software                                             |   |    |   |           | 17  |

|    | 2.1    | Introduction                                         |   |    |   |           | 17  |

|    | 2.2    | Background                                           |   |    |   |           | 21  |

|    |        | 2.2.1 Refinement Type Systems                        |   |    |   |           | 21  |

|    |        | 2.2.2 Cache Hierarchy and Cache Side-channels        |   |    |   |           | 22  |

|    |        | 2.2.3 Cache Side Channel Mitigation                  |   |    |   |           | 23  |

|    | 2.3    | Research Overview                                    |   |    |   |           | 24  |

|    |        | 2.3.1 Assumptions                                    |   |    |   |           | 24  |

|    |        | 2.3.2 Methodology Overview                           | • |    |   |           | 25  |

|    | 2.4    | Design                                               |   |    |   |           | 30  |

|   |            | 2.4.1  | Bit-level Representation and Types                                                                                            |

|---|------------|--------|-------------------------------------------------------------------------------------------------------------------------------|

|   |            | 2.4.2  | Type Inference for Bitvectors    33                                                                                           |

|   |            | 2.4.3  | Type Inference Rules    34                                                                                                    |

|   |            | 2.4.4  | Cache Side-channel Detection                                                                                                  |

|   | 2.5        | Imple  | $mentation \dots \dots$ |

|   | 2.6        | Evalua | $ation \dots \dots$     |

|   |            | 2.6.1  | Evaluation Setup                                                                                                              |

|   |            | 2.6.2  | Results Overview                                                                                                              |

|   |            | 2.6.3  | Discussion of Known Vulnerabilities                                                                                           |

|   |            | 2.6.4  | Unknown Vulnerabilities                                                                                                       |

|   |            | 2.6.5  | Discussion about Blinding 56                                                                                                  |

|   |            | 2.6.6  | Reducing False Positives                                                                                                      |

|   | 2.7        | Discus | sion and Limitation                                                                                                           |

|   | 2.8        | Relate | d Work                                                                                                                        |

|   | 2.9        | Conclu | 1sion                                                                                                                         |

|   |            |        |                                                                                                                               |

| 3 |            |        | aided Mitigation against Side-channels in Trusted Exe-                                                                        |

|   |            |        | vironment 65                                                                                                                  |

|   | 3.1        |        | uction                                                                                                                        |

|   | 3.2        | -      | $round \dots \dots$     |

|   |            | 3.2.1  | Ciphertext Side-channel Attacks                                                                                               |

|   |            | 3.2.2  | Countermeasures to Ciphertext Side-channels                                                                                   |

|   | 3.3        |        | odology Overview                                                                                                              |

|   |            | 3.3.1  | Threat Model                                                                                                                  |

|   |            | 3.3.2  | A Motivating Example                                                                                                          |

|   |            | 3.3.3  | Motivations of Compiler-aided Mitigation                                                                                      |

|   |            | 3.3.4  | Architecture Overview of CIPHERGUARD                                                                                          |

|   | <b>.</b>   | 3.3.5  | Technical Challenges    78                                                                                                    |

|   | 3.4        |        | ed System Design                                                                                                              |

|   |            |        | Tainting Secret Locations   80     C. G. Locations   81                                                                       |

|   |            | 3.4.2  | Software-based Probabilistic Encryption                                                                                       |

|   |            | 3.4.3  | Secret-aware Register Allocation                                                                                              |

|   | 0 <b>-</b> | 3.4.4  | Managing Nonce Buffers                                                                                                        |

|   | 3.5        |        | $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                          |

|   | 3.6        |        | $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                          |

|   |            | 3.6.1  | Experiment Setup                                                                                                              |

|   |            | 3.6.2  | Comparison between Variants                                                                                                   |

|   |            | 3.6.3  | Comparison with CIPHERFIX                                                                                                     |

|   |            | 3.6.4  | Comparison with OBELIX                                                                                                        |

|   | o =        | 3.6.5  | Security Analysis                                                                                                             |

|   | 3.7        |        | 104                                                                                                                           |

|   | 3.8        | Conch  | 1sion                                                                                                                         |

| 4  | Nor             | interfe | erence-based Verification of Side-channels in Microa | r-    |

|----|-----------------|---------|------------------------------------------------------|-------|

|    | $\mathbf{chit}$ | ectura  | l Designs                                            | 107   |

|    | 4.1             | Introd  | uction                                               | . 107 |

|    | 4.2             | Backg   | round                                                | . 110 |

|    |                 | 4.2.1   | Cache Side-channel Attacks                           | . 110 |

|    |                 | 4.2.2   | Mutual Information                                   | . 112 |

|    |                 | 4.2.3   | Isabelle/HOL                                         | . 113 |

|    | 4.3             | Metho   | odology Overview                                     | . 113 |

|    |                 | 4.3.1   | Threat Model                                         | . 113 |

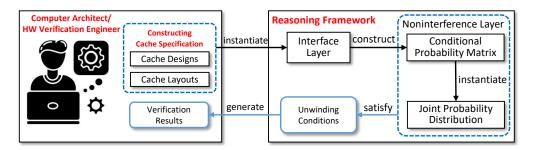

|    |                 | 4.3.2   | Architecture                                         | . 114 |

|    |                 | 4.3.3   | Available Proving Technique                          | . 116 |

|    | 4.4             | Design  | of Reasoning Framework                               | . 116 |

|    |                 | 4.4.1   | An Abstract State Machine                            | . 117 |

|    |                 | 4.4.2   | Noninterference                                      | . 118 |

|    |                 | 4.4.3   | Unwinding Conditions                                 |       |

|    | 4.5             | Applic  | eation of Our Methodology                            |       |

|    |                 | 4.5.1   | Verifying Cache Designs                              |       |

|    |                 | 4.5.2   | Verifying TLB Designs                                |       |

|    | 4.6             | Evalua  | ation                                                |       |

|    | 4.7             |         | usion                                                |       |

| 5  | Con             | clusio  | ns and Future Work                                   | 135   |

|    | 5.1             | Conclu  | usions                                               | . 135 |

|    | 5.2             | Future  | e Work                                               | . 136 |

| Li | st of           | Autho   | or's Awards, Patents, and Publications               | 139   |

| Bi | bliog           | raphy   |                                                      | 141   |

# List of Figures

| 2.1  | Square-and-Multiply Exponentiation                                                   |

|------|--------------------------------------------------------------------------------------|

| 2.2  | Sliding-window Exponentiation                                                        |

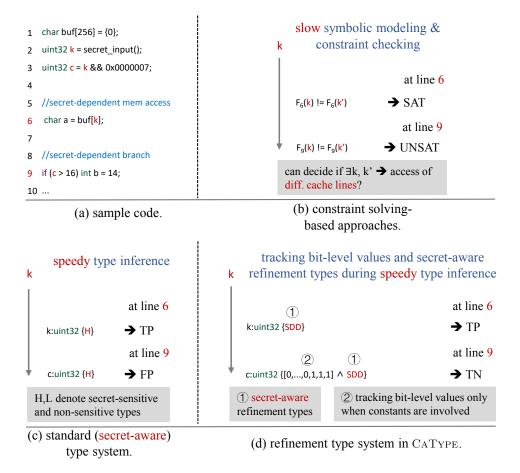

| 2.3  | Comparison of constraint solving-based techniques (b), type inference-               |

|      | based approach (c), and CATYPE (d). TP, FP, and TN denote true                       |

|      | positive, false positive, and true negative, respectively                            |

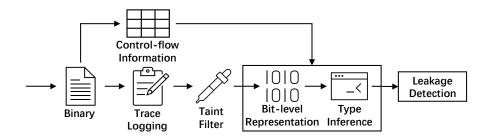

| 2.4  | Workflow of CATYPE                                                                   |

| 2.5  | Syntax of bit-level representation                                                   |

| 2.6  | Type propagation from single-bit to bitvector                                        |

| 2.7  | One-bitvector Constant Type Rules                                                    |

| 2.8  | One bit B type rules for logical operations                                          |

| 2.9  | Type rules for expressions involving bitvector $\operatorname{Vec}\langle n \rangle$ |

| 2.10 | Type Rules for Statements                                                            |

| 2.11 | BN_num_bits_word                                                                     |

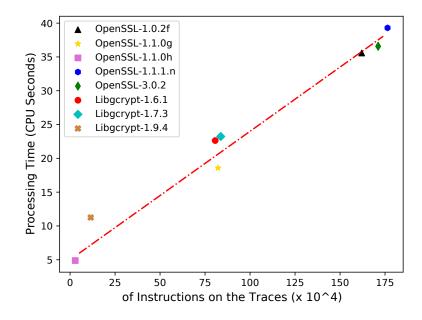

| 2.12 | Trace lengths/processing time towards the analysis of RSA imple-                     |

|      | mentations                                                                           |

| 2.13 | RSA/ElGamal information leaks found in Libgcrypt-1.6.1 49                            |

| 2.14 | RSA information leaks found in OpenSSL-1.0.2f                                        |

| 2.15 | Window size of modular exponentiation                                                |

|      | ECDSA information leaks found in OpenSSL-1.1.0g                                      |

| 2.17 | Bignumber resize                                                                     |

|      | Window size selection                                                                |

| 2.19 | BN_rshift1 information leaks found in OpenSSL-1.1.0g                                 |

| 2.20 | bn_mul_normal information leaks found in OpenSSL-1.1.0i 55                           |

| 2.21 | BN_copy from the OpenSSL Library                                                     |

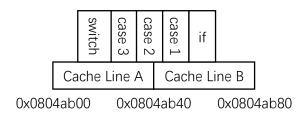

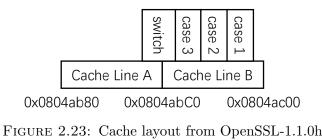

| 2.22 | Cache layout from OpenSSL-1.1.0g 57                                                  |

| 2.23 | Cache layout from OpenSSL-1.1.0h                                                     |

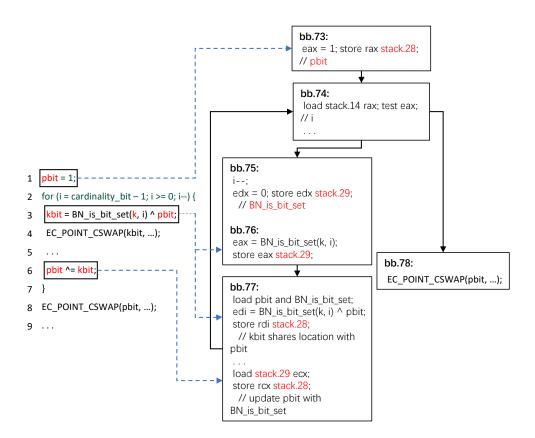

| 3.1  | ossl_ec_scalar_mul_ladder                                                            |

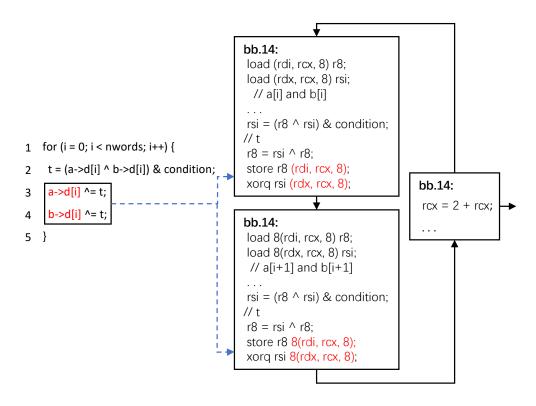

| 3.2  | BN_constant_swap                                                                     |

| 3.3  | ossl_ec_scalar_mul_ladder and its Machine Basic Block 73                             |

| 3.4  | BN_constant_swap and its Machine Basic Block                                         |

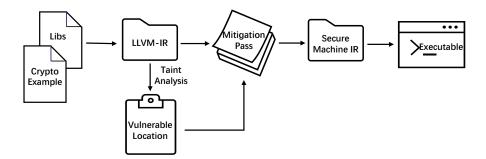

| 3.5  | Workflow of CIPHERGUARD                                                              |

| 3.6  | In-place code insertion                                                              |

| 3.7  | Sensitive stack slots contained in MBBs                                              |

|      |                                                                                      |

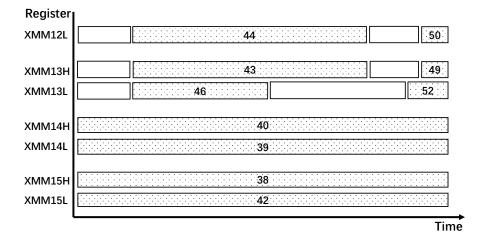

| 3.8  | An example of register allocation from the function <b>bn_mul_add_words</b> of OpenSSL-ECDSA. In the visualization, the white and shaded     |     |

|------|----------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | blocks represent the liveness of stacks, with shaded blocks contain-<br>ing numbers that denote registers holding the sensitive stack slots. | 86  |

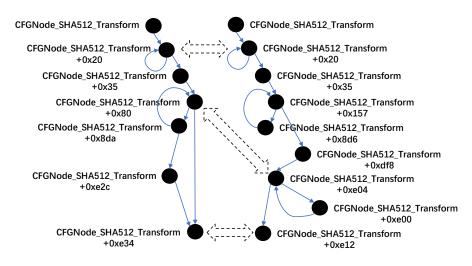

| 3.9  | Function SHA512_Transform from the libsodium-SHA512 serves as<br>an example to illustrate the construction of CFGs and identify crit-        |     |

|      | ical nodes.                                                                                                                                  | 97  |

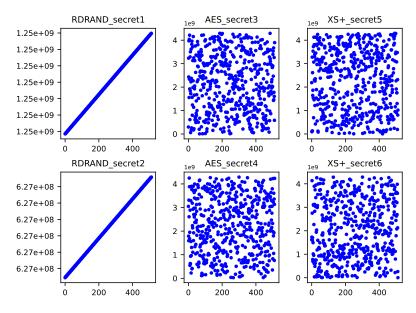

| 3.10 | Scatter distribution of masked <i>pbit</i> under different variants. Each secret sequence comprises 512 values.                              | 102 |

| 3.11 | A corner case arises when a one-bit change in the secret can be re-<br>vealed by observing identical masked plaintext across multiple mask-  |     |

|      | ing                                                                                                                                          | 103 |

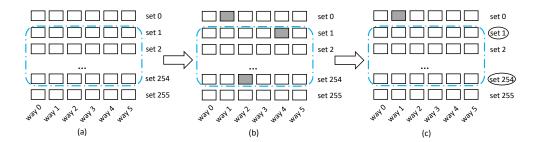

| 4.1  | Side-channel attack scheme. Sub-figure (a) represents the prepara-                                                                           |     |

|      | tion phase, (b) the waiting phase, and (c) the observation phase                                                                             | 111 |

| 4.2  | Workflow of our proposed approach.                                                                                                           | 115 |

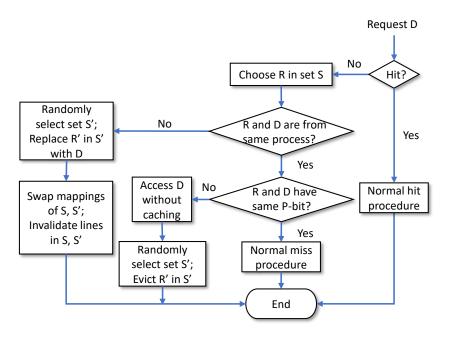

| 4.3  | Workflow of Random Permutation Cache                                                                                                         | 124 |

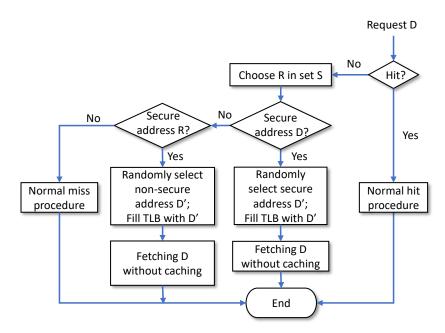

| 4.4  | Workflow of Random Fill TLB                                                                                                                  | 129 |

# List of Tables

| 2.1 | Type inference over sample assembly code. To ease reading, we use $K = 1$ W and U to terms reference trues predicates corresponding                                                                             |     |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|     | K, I, W, and U to term refinement type predicates, corresponding to SDD, SID, WRA, and URA types. $\{K\}^{32}$ means bit K repeats                                                                              |     |

|     | 32 times, while $\{1\}^{16}$ means bit 1 repeats 16 times. "c-line" stands                                                                                                                                      |     |

|     | for cache line.                                                                                                                                                                                                 | 41  |

| 2.2 | Cryptosystems analyzed by CATYPE                                                                                                                                                                                | 44  |

| 2.3 | Identified Information Leakage Sites/Units by CATYPE. We com-<br>pare the results with recent works, including CacheD, CacheS and                                                                               |     |

|     | DATA                                                                                                                                                                                                            | 45  |

| 2.4 | Performance comparison with CacheD/CacheS. We also list the anal-<br>ysis of eight RSA implementations for scalability assessment                                                                               | 48  |

| 2.5 | Branch vulnerabilities identified by CATYPE under gcc -00, -02, and -03 optimization settings.                                                                                                                  | 59  |

| 2.6 | Checking the correctness of refinement type system in CATYPE by<br>comparing with taint analysis. "FPs" denotes false positives of taint<br>analysis. We randomly select 100 cases for each setting for confir- |     |

|     | mation except ElGamal/Libgcrypt 1.9.4.                                                                                                                                                                          | 61  |

| 3.1 | The maximum numbers of sensitive stack slots among tainted func-                                                                                                                                                |     |

| 0.1 | tions.                                                                                                                                                                                                          | 84  |

| 3.2 | Performance statistics towards mitigated cryptography software with 3 variants of CIPHERGUARD. Results are obtained by measuring the average clock cycles using the rdtsc instruction. XS+ is short for         | 01  |

|     | XorShift128+                                                                                                                                                                                                    | 91  |

| 3.3 | Performance improvement by Variant 1 over the on-the-fly rdrand                                                                                                                                                 |     |

|     | method. CC20 is short for ChaCha20.                                                                                                                                                                             | 93  |

| 3.4 | Profit analysis of variant 3                                                                                                                                                                                    | 94  |

| 3.5 | Performance comparison with CIPHERFIX based on the same num-                                                                                                                                                    |     |

|     | ber of tainted functions. The replication of CIPHERFIX is conducted                                                                                                                                             |     |

|     | on its FAST version                                                                                                                                                                                             | 96  |

| 3.6 | Performance comparison between OBELIX and CIPHERGUARD. The                                                                                                                                                      |     |

| ~ - | factor data comes from OBELIX paper and Table 3.2.                                                                                                                                                              | 100 |

| 3.7 | Entropy of the secret distribution under different variants. For each                                                                                                                                           |     |

|     | variant, we run the cryptography library twice to ensure that the                                                                                                                                               | 100 |

|     | original secrets are different                                                                                                                                                                                  | 102 |

| 4.1 Verification Results of Cache Designs. | 132 |

|--------------------------------------------|-----|

|--------------------------------------------|-----|

# Symbols and Acronyms

# Symbols

| H                                     | the high security sensitivity of data                               |

|---------------------------------------|---------------------------------------------------------------------|

| L                                     | the low security sensitivity of data                                |

| T                                     | the basic type                                                      |

| P                                     | the predicate associated with the basic type                        |

| #                                     | the concatenation operation of two expressions                      |

| $[n_1:n_2]/\cdot$                     | the extraction operation of the designated position of a bitvector  |

|                                       | expression                                                          |

| $\bowtie$                             | the logic operations                                                |

| $\operatorname{Vec}\langle n \rangle$ | the bitvector of $n$ bits                                           |

| $\Box$                                | the operation of taking the least upper bound of two types          |

| $  x  _t$                             | the operation of inferring a bitvector's type from the types of its |

|                                       | constituent bits based on a notion of structural priority           |

| K                                     | the abbreviation of SDD type                                        |

| Ι                                     | the abbreviation of SID type                                        |

| W                                     | the abbreviation of WRA type                                        |

| U                                     | the abbreviation of URA type                                        |

| $\{\cdot\}^n$                         | the n-time repetitions of a bit                                     |

|                                       |                                                                     |

| $\mathcal{X}$                         | the probability distribution of input                               |

| ${\mathcal Y}$                        | the probability distribution of output                              |

| $\mathbb{P}(\cdot	imes\cdot)$         | the power-set of two types                                          |

| ${\mathcal I}$                        | the input content                                                   |

| $\mathcal{O}$                         | the output content                                                  |

| ${\cal P}$                            | the probability in real type                                        |

| $\psi$                                | the event-state transition function                                 |

|                                       |                                                                     |

| $\overline{\omega}$ | the output function                             |

|---------------------|-------------------------------------------------|

| S                   | the state space                                 |

| ${\cal E}$          | the set of event labels                         |

| $\mathcal{M}$       | the abstract state machine                      |

| Cpt                 | the conditional probability transition function |

| ${\mathcal W}$      | the conditional probability matrix              |

| ${\mathcal J}$      | the joint distribution                          |

## Acronyms

| IoT   | Internet of Things                       |

|-------|------------------------------------------|

| TEE   | Trusted Execution Environment            |

| TLB   | Translation Lookaside Buffer             |

| DRAM  | Dynamic Random Access Memory             |

| PTE   | Page Table Entry                         |

| SPA   | Simple Power Analysis                    |

| DPA   | Differential Power Analysis              |

| DES   | Data Encryption Standard                 |

| SEMA  | Simple Electromagnetic Analysis          |

| DEMA  | Differential Electromagnetic Analysis    |

| LLC   | Last Level Cache                         |

| CAT   | Cache Allocation Technology              |

| VM    | Virtual Machine                          |

| ORAM  | Oblivious Random Access Memory           |

| TSX   | Transactional Synchronization Extensions |

| SSA   | Static Single Assignment                 |

|       |                                          |

| SDBC  | Secret-Dependent Branch Condition        |

| SDMA  | Secret-Dependent Memory Access           |

| SAT   | Satisfiability                           |

| UNSAT | Unsatisfiability                         |

| SDD   | Secret-Dependent Distribution            |

| URA   | Uniformly Random Distribution            |

| SID   | Secret-Independent Distribution          |

| WRA   | Weakly Random Distribution               |

|       |                                          |

| CST        | Constant                           |

|------------|------------------------------------|

| MA         | Memory Access                      |

| BC         | Branch Condition                   |

| ТР         | True Positive                      |

| FP         | False Positive                     |

| TN         | True Negative                      |

| <b>ODV</b> |                                    |

| SEV        | Secure Encryption Virtualization   |

| ES         | Encrypted State                    |

| SNP        | Secure Nested Paging               |

| SGX        | Software Guard Extension           |

| TDX        | Trust Domain Extension             |

| CCA        | Confidential Compute Architecture  |

| NPT        | Nested Page Table                  |

| ASID       | Address Space identifier           |

| DFSan      | Data Flow Sanitizer                |

| XEX        | XOR-Encrypt-XOR                    |

| MBB        | Machine Basic Block                |

| SIMD       | Single Instruction Multiple Data   |

| CFG        | Control Flow Graph                 |

| ORAM       | Oblivious RAM                      |

| ASLR       | Address Space Layout Randomization |

| IIDI       |                                    |

| HDL        | Hardware Description Language      |

| MMU        | Memory Management Unit             |

| VA         | Virtual Address                    |

| PA         | Physical Address                   |

| SA         | Set Associative                    |

| RP         | Random Permutation                 |

| RF         | Random Fill                        |

| PL         | Partition Locked                   |

| NO         | No Observation                     |

| CO         | Constant Observation               |

|            |                                    |

### Chapter 1

## Introduction

#### 1.1 Side-channel Attacks

Side-channel attacks present a serious risk to computer security, leveraging subtle information leaks that occur during routine system operations. By exploiting unintended side effects such as power usage, electromagnetic emissions, and variations in execution times, malicious actors can deduce critical data such as encryption keys, passwords, and other sensitive information. These attacks are difficult to detect because they operate outside traditional intrusion methods, making them particularly stealthy. Currently, side-channel attacks have proven effective against both software and hardware, affecting a wide array of devices, from smartphones and Internet of Things (IoT) devices to highly secure servers.

Side-channel attacks encompass micro-architectural attacks, power attacks, electromagnetic attacks, fault attacks, and transient execution attacks. Notably, the attack and defense research on micro-architectural side-channels has advanced considerably in recent years. Moreover, with the rise of trusted computing and the application of Trusted Execution Environments (TEEs), research targeting sidechannel attacks on TEEs has also emerged. Below, we offer a concise overview of side-channel attacks in different contexts.

#### 1.1.1 Micro-architectural Side-channels

Micro-architectural side-channel attacks represent a significant and particularly insidious subset of side-channel attacks that exploit the behavior of a computer's hardware optimizations [1].

Conventional attacks. Initially, timing side-channel attacks were first utilized to compromise cryptography software by observing the execution time of operations involving private keys [2]. Over time, attention shifted to cache side-channel attacks, where attackers meticulously measure the access time to specific cache locations to deduce patterns and infer activities within the targeted system [3–8]. These attacks can expose sensitive details such as secret-dependent control-flow patterns and memory access patterns [9–14]. Cache side-channel attacks are noted for their ability to operate stealthily at a low level, posing significant challenges for detection and defense.

Subsequently, more optimizations in modern processors and operating systems have been exploited to obtain side-channel information. For instance, the branch predictor unit, which forecasts branch outcomes and pre-processes subsequent code, does not clear its values during context switches, potentially exposing sensitive data [15– 17]. Another critical optimization unit is the Translation Lookaside Buffer (TLB), which stores mappings from virtual addresses to physical addresses. Attackers can exploit the TLB to ascertain if a specific page is recently accessed, thus inferring sensitive data [18].

Furthermore, additional optimizations including the memory management unit [19, 20], floating-point units [21], CPU ring interconnect [22], CPU ports [23, 24], and the random number generator [25] introduce variations in the program execution time, thereby exposing confidential information.

Fault attacks. Fault attacks exploit physical phenomena and are considered active attacks, where attackers manipulate hardware components beyond their intended limits using software. These exploits capitalize on vulnerabilities in the physical design of computer hardware, such as Dynamic Random Access Memory (DRAM), to compromise system security. One well-known fault attack is Rowhammer, which targets DRAM [26–41]. Specifically, in DRAM, each cell stores binary data (0 or 1) using a capacitor and transistor. Through repeated access to these cells, electrical charge can leak, causing unintended interactions with nearby cells. This

phenomenon induces bit flips in adjacent memory cells without direct access, potentially altering critical data and compromising system integrity. Rowhammer exemplifies how subtle manipulations of hardware at the physical level can lead to significant security risks, highlighting the intricate nature and stealthiness of fault attacks in computing environments.

**Transient execution attacks.** Transient execution attacks exploit instructions that are not permanently committed in the architectural state due to speculative execution mis-predictions or faults. Despite pipeline flushes ensuring functional correctness by discarding any architectural effects, traces persist in the micro-architecture [42]. Techniques for extracting information from these traces through side channels have been significantly refined over the past decade. Transient execution attacks are classified into two types: Meltdown and Spectre attacks [43, 44]. Meltdown attacks involve exploiting transient reads from L1 data caches or fill buffers to retrieve secrets, while Spectre attacks use branch predictors and the return stack buffer to induce branch mis-predictions. These attacks pose greater risks compared to conventional side channels and fault attacks, capable of leaking sensitive data such as kernel memory and passwords.

#### 1.1.2 Trusted Computing Side-channels

Major processor vendors introduce a hardware-based technology known as TEE, which provides an isolated environment with memory encryption to fortify the integrity and confidentiality of Virtual Machines (VMs) against privileged attackers, such as malicious hypervisors or host OS. Micro-architectural side-channel attacks within TEE represent a prominent area of security research. Similar to traditional side-channels, this domain focuses on various micro-architectural components in TEE.

For instance, Dessouky et al. [45] demonstrated that timing analysis on caches can uncover sensitive data within TEEs. Building on previous work, the Prime+Count cache side-channel attack was introduced against ARM TrustZone [46]. For TLB component, Gras et al. [18] identified that attackers could exploit the TLB to determine if a specific page was recently accessed in a TEE, thereby obtaining sensitive data, with TLSBleed serving as an example. Additionally, Lee et al. [47] utilized the branch target buffer to execute the Branch Shadowing attack, while Evtyushkin et al. [17] exploited directional branch predictors to infer sensitive information by causing branch conflicts. Moreover, page-fault side-channel attacks allowed attackers to deduce control and data flows from page faults [48]. These attacks are classified based on the Page Table Entry (PTE) flag being monitored, such as the present, accessed, dirty, and reserved bits [49]. DRAM side-channel attacks exploited timing variations during memory operations, enabling attackers to discern memory access patterns in TEEs [50]. Meltdown attacks leveraged transient reads from L1 data caches or fill buffers to extract TEE secrets, with notable examples including the Foreshadow attack [51], Cache Line Freezing attack [52], and ZombieLoad attack [53]. Spectre attacks leveraged branch mis-predictions, including SgxPectre [54], which used branch predictors, and SpectreRSB [55], which employed the return stack buffer.

Notably, researchers have discovered a new side-channel called ciphertext sidechannel attack due to the deterministic memory encryption used in AMD's TEE. This attack allows an attacker to deduce relationships between successive plaintexts or identify specific plaintext patterns by observing changes in ciphertexts. The concept of ciphertext side channels was first introduced in Li et al's work [56] and further explored by systematically examining the applicability of this vulnerability [57]. While the initial research focused on AMD's TEE [58], it is important to note that this vulnerability also affects other TEE architectures based on deterministic encryption, provided that attackers can access ciphertext (through software access [56] or memory bus snooping [59]).

#### 1.1.3 Physical Side-channels

Power attacks and electromagnetic attacks are both non-invasive side-channel attacks, meaning the attacker measures various energy consumption or electromagnetic emissions of cryptography hardware devices. These side-channel attacks are effective because bit flips in data cause changes in energy consumption or electromagnetic emissions, allowing the attacker to infer the key.

Power attacks are mainly divided into two types: Simple Power Analysis (SPA) [60, 61] and Differential Power Analysis (DPA) [62, 63]. SPA examines the waveform of current or power consumption over time, using the values of energy consumption to

infer related confidential information. Different instructions executed in a microprocessor generate different currents and power consumption, enabling attackers to deduce the control-flow information of the running program through power supply analysis. Thus, control-flows in cryptography systems that depend on the key are prime targets for attackers. For example, in the RSA cryptosystem, the sequence of square and multiply operations depends on the bit values of the key, making it a focal point for side-channel attacks. DPA is a more advanced power analysis technique that performs statistical analysis on data collected from multiple encryption and decryption operations to calculate intermediate values during computation. DPA relies on the assumption that in a cryptography system, there is an intermediate variable where part of the key's bit values determine whether two inputs will result in the same value for this variable. DPA does not focus on individual power consumption information, thus making it less susceptible to noise. By observing the S-box operations in the Data Encryption Standard (DES) cryptosystem, DPA can recover several key bit values.

Similar to power attacks, electromagnetic attacks derive sensitive information from cryptography systems by measuring the electromagnetic emissions of hardware devices. Electromagnetic attacks are also categorized into Simple Electromagnetic Analysis (SEMA) and Differential Electromagnetic Analysis (DEMA) [64, 65], following the same principles as power analysis counterparts.

Fault injection side-channel attacks involve altering the normal logic of a device through external interference, causing the cryptography system to enter an exploitable error state, thereby revealing internal states, sensitive information, or even the key. These attacks manipulate the operation of cryptography hardware devices by changing the temperature, voltage, clock frequency, magnetic field strength, or by emitting electromagnetic pulses and lasers, thus disrupting the processor's operation and causing it to produce incorrect results. For example, during encryption or decryption, random errors in the hardware device's registers or memory can cause a bit flip. By comparing the correct ciphertext with the erroneous ciphertext or observing the system's state, attackers can theoretically analyze and crack the sensitive information of the cryptography system. Studies have shown that fault injection attacks can successfully break DES and triple DES keys by flipping just 200 bits [66].

#### 1.2 Side-channel Mitigation

#### **1.2.1** Secure Architectures and System Designs

A number of works aim to defeat side channels from both software and hardware perspectives. We describe their mechanisms with cache side-channel attacks as an example. In short, their purposes are divided into two categories based on the strategies, namely limiting attacker's abilities (thus limiting attacker's observation) and obfuscating attacker's observation.

Limiting attacker's abilities. Specifically, designing partition-based cache circuits strongly guaranteed hardware isolation [67, 68], whereas there is a long way to go before adopting these new cache designs to commercial CPUs. Software-level cache partition is then much more practical to achieve. For instance, employing the page coloring mechanism [69, 70], where the same memory page color can be mapped into the same cache set, partitioned the use of the Last-level-Cache (LLC) for different security domains, thus excluding any possible cache conflicts. A similar approach to PLcache [67] was implemented by stealth memory technique [71] through offering hypercalls to lock stealth pages, which are never evicted out of the cache. Besides, the Cache Allocation Technology (CAT) [72] was employed to divide the LLC into secure and non-secure partitions [73]. The non-secure partition is managed as a normal cache while the secure partition only stores secure pages of a user-level program, hence cache line conflicts to secure pages are invisible to attackers. Similarly, Zhou et al. [74] managed the number of lines per cache set that an attacker may probe, weakening the attacker's ability to control the cache. Although the partition mechanism strongly confines an attacker's observation, it is at the cost of cache utilization and performance degradation.

Another approach to limiting attackers' abilities is to restrict their preemption or occupation to caches through a scheduler mechanism, especially in the Cross-VM context. Godfrey et al. [75] and Sprabery et al. [76] relied on scheduler operations to flush cache contents when switching a VM in the cloud, achieving temporal partition of caches. Another work from Varadarajan et al. [77] leveraged the hypervisor scheduler to limit the frequency of cache preemption, obfuscating predictive state to attackers. Nevertheless, relying on the scheduling approach to achieve temporal isolation of cache is still problematic because latency-sensitive workloads may be delayed.

**Obfuscating attacker's observation.** An attacker fails to deduce secrets when he obtains invalid observations. Motivated by this idea, novel randomization-based cache components were proposed to randomize the resident points of data in the cache, achieving a high entropy for each data unit [67, 78–80]. However, recent studies showed that these randomization-based caches are still vulnerable to cache side-channel attacks [81, 82].

By increasing difficulty to the adversary's measurements and resulting in a fixed or random observation, it becomes infeasible for the adversary to obtain accurate timing information. For example, Aviram et al. [83] provided enforced deterministic execution to eliminate timing channels. Another two works [84, 85] modified the *rdtsc* instruction to offer coarse-grained clocks and added a small randomized offset to fuzz the guest operating system's measurement, respectively. Extremely, Li et al. [86] introduced three replication of a VM and normalizes the timing to be observed by the median of replicas collectively determined. The above three works [84–86] disabled precise timing measurement for mitigating timing-channel attacks, yet severely limiting the workloads that need accurate timing and may incur overheads for network workloads resident in the cloud. In contrast, Zhang et al. [87] periodically injected noise through flushing the L1 cache among the adversary's waiting period to obfuscate his timing measurement.

Software diversity aimed to prevent the adversary's observation from deducing a predictable cache state [26, 74, 88–90]. Precisely, Liu et al. [88] leveraged compiler transformation to guarantee memory access traces are the same no matter which control flow path is taken by the program. Later, Rane et al. [89] made improvements by arranging the exact same instructions for both paths of a branch, preventing a wider range of side channels. Without modifying the source codes, Grane et al. [90] dynamically inserted a mass of redundant operations (e.g., *nop* and memory load) to generate diversified replicas, thus randomizing the control flow of programs. Disabling and selectively enabling memory page sharing were proposed to separate the touched points in the cache [26, 74]. As memory deduplication drives the access requests to the shared libraries from two distinct programs into the same cache line, the attacker cannot deduce whether a certain path is executed by the victim program from his observation.

#### 1.2.2 Trusted Computing Hardening

Since TEEs are built upon CPU hardware security technologies, vulnerabilities at the micro-architectural level and flaws in the architectural design can severely compromise the security of TEEs. Researchers have extensively explored architectural security enhancements, driving the iteration of TEE architectures.

To defend against micro-architectural side-channel vulnerabilities, the primary mechanisms are implemented through software, focusing on detecting the occurrence of side-channel activities and disrupting the acquisition of side-channel information. Given that micro-architectural side-channel attacks often involve frequent interrupts, detecting these interference signals can help identify ongoing attacks [91, 92]. Additionally, since frequent interrupts result in increased latency for TEE operations, some approaches used this latency as an indicator of an attack [93]. Providing an uninterrupted execution environment for TEEs is also a crucial defensive measure against side-channel attacks. For example, Chen et al. [94] ensured an uninterrupted environment through verifiable execution contracts. To prevent attackers from obtaining effective side-channel information, current defenses utilized Oblivious RAM (ORAM) [95, 96], CPU hardware features like Transactional Synchronization Extensions (TSX) [97–99], and the introduction of randomization techniques [100].

Transient execution vulnerabilities can be further divided into those caused by implementation flaws and those resulting from design flaws. The former is due to improper implementation of the CPU's exception handling mechanisms and has been addressed by hardware patches and upgrades in mainstream processors. The latter is related to branch prediction units and represent design flaws, requiring longer deployment cycles for hardware-based fixes [101]. The current mainstream solution involves compiler-assisted software hardening, although this often incurred significant performance overhead [102].

#### **1.2.3** Constant-time Principles

Constant-time is a critical concept to resist side-channel leakage, which inherently requires the memory access and condition branch to be independent of the secrets. Constant-time verification. Prior works develop analysis to formally reason the constant-time designs, with more and more precise leakage models. In the early stages, researchers applied a policy called program counter [103–108], where it only takes into account the critical control flow and balances the timing behavior of both branches. Considering memory accesses, subsequent works abided by the most common leakage model that exploits time variations and covers cache-based attacks. Specifically, VirtualCert [109] and constant-time MEE-CBC [110] performed typing analysis in CompCert [111] on the x86 assembly, which enforced the notion of noninterference to verify the classic observation equivalent. Similarly, FlowTracker [112] analyzed the Static Single Assignment (SSA) form for LLVM programs. Later, variable-time operations are also taken into account by Dehesa-Azuara et al. [113]. They relaxed the conventional noninterference, where the observation can be the execution time or cache side channels.

In addition to noninterference, the reduction-based methods were applied, where security was reduced to safety through the self-composition of programs or formulas [114–120]. Separately, Almeida et al. [114] performed deductive verification based on self-composition on C implementations, while ct-verif [115] targeted the optimized LLVM implementations. A variety of methods, such as Themis [116], Blazer [117], and IFC-CEGAR/BMC [118], were proposed to improve the selfcomposition through taint analysis or complexity analysis. Different from ctverif [115] that utilized solvers to prove safety implying constant-time property, Blazy et al. [119] developed an analyzer based on abstract interpretation to compute the approximation of the execution of the analyzed program in an instrumented semantics with tainting. Recently, considering the constant-time properties were generally not preserved by the compilation, Binsec/rel [120] proposed a relational symbolic execution-based analysis tool for verifying constant-time implementations at the binary level. It self-composed the formulas of the program execution and maximized sharing the equal expressions in both executions for improving the performance of reduction.

**Constant-time construction.** The main target of this category is to formally construct high-assurance cryptography libraries that fundamentally resolve the constant-time issues. However, this is only restricted to the verified code level instead of the runtime. For example,  $F^*$  [121] and HACL\* [122] (also bases on  $F^*$

language [123]) both supplied verified cryptography libraries at the source level. Differently, the former [121] enforced a coding discipline for mitigating side channels by typing checking, while HACL\* [122] proved freedom of timing channels through manual pre-postconditions that at large rely on experts. In such a way, they suffer from limited scalability. Moreover, their verification toolchain stops at the source code, thereby failing to promise secret independence properties delivered to lower code when using mainstream compilers. Vale [124] impelled the progress of constructing side-channel freedom of a cryptography program to an assemblylike code, i.e., Vale language. The Vale leakage verifier employed a taint-analysis engine and the self-composition method to verify the program's freedom from sidechannel vulnerabilities. However, Vale shared the same drawback that thinking of the compiler as trusted thus not verifying it. Jasmin [125] and Fact [126] were compiler-based formal frameworks that respectively transform Jasmin programs into assembly code, and timing-sensitive FaCT code into constant-time LLVM IR.

Constant-time transformation. Transforming programs into constant-time equivalents or variations also plays a significant role. Johan Agat [103] and Kopf et al. [106] equalized the timing characteristics of secret-dependent conditional branches by inserting dummy statements that do not update global variables, while Barthe et al. [105] transformed two branches into the form of transaction. Using source-to-source transformation, Molnar et al. [104] consecutively executed secretdependent branches and leverages bit-masking to commit the correct results. Similarly, Coppens et al. [127] executed the dummy path with local, temporary variables and submitted results with conditional instructions. Nevertheless, all these works only consider branches that are under a simple side-channel attack model, i.e., program counter security [104]. This means the branches of a balanced time property may still leak the secrets with more-capable attackers such as cache-based attacks. In addition, Barthe et al. [128, 129] proved the observational noninterference of a compilation process, guaranteeing the constant-time property for cryptography. Concretely, CompCert [111] was modified to enable it to capture constant-time during the compilation [129]. Recently, SC-Eliminator [130] removed secret-dependent branches by both executing real and decoy paths. However, its way to preloading the lookup table cannot completely eliminate the cache side channels because the table may be evicted by the attacker. Considering the unmodified addresses in the decoy path that may result in out-of-bounds memory accesses in SC-Eliminator, Soares et al. [131] guaranteed memory-safe accesses in the decoy paths. For the

decoy iterations, they both inferred a bounded loop number from the compilation and unroll the loop, hence the code size increases [130, 131]. Constantine [132], like the most radical method in constant-time, proposed the linearization of controlflow and data-flow, meaning to execute all possible code/data memory accesses. It improved the linearization of loops by just-in-time the number that the loop should execute. Nevertheless, Constantine only guaranteed the transformed code is constant-time and required subsequent compilation not to add branches, which may break the constant-time.

#### **1.3** Research Scope and Overview

Researchers have made significant strides in defeating side-channels by developing innovative hardware-based defenses and implementing software-level countermeasures, thus enhancing the security of modern computing systems.

While there is a growing body of work dedicated to the detection of cache sidechannels, many of these efforts grapple with significant challenges in terms of comprehensiveness and scalability. Detecting cache side-channels is inherently complex due to the intricate interplay between hardware, software, and micro-architectural intricacies. This complexity often results in a lack of comprehensiveness of the underlying mechanisms and vulnerabilities, which can hinder the effectiveness of detection methods. For example, CacheD [133] employed symbolic execution on tainted assembly code to construct formulas, which were then sent to a solver to check whether a memory address maps to different cache locations, depending on secret values. However, CacheD primarily focused on secret-dependent memory accesses and overlooked branches in its analysis. Additionally, the scalability of cache side-channel detection approaches is a pervasive concern. Cryptography systems become increasingly intricate and larger in scale, making it challenging to apply existing detection techniques comprehensively. One example is that modern cryptography libraries extensively use randomization techniques, such as blinding, to mitigate side-channel attacks. However, the effectiveness of these techniques (and any remaining information leaks) has not been analyzed by previous tools like CacheS [134], which is considered one of the most scalable static analysis tools

in this field. Consequently, addressing these issues in cache side-channel detection is paramount, as it ensures that security efforts remain effective in the face of evolving threats and complex computing infrastructures.

It is important to highlight that while constant-time coding practices have traditionally been an effective means of mitigating cache side-channels, their efficacy wanes when dealing with new challenges posed by ciphertext side channels. In short, ciphertext side-channel attacks exploit the deterministic memory encryption employed by TEEs, where the same physical address consistently encrypts into the same ciphertext block. This inherent determinism means that constant-time coding practices, which traditionally neutralize timing variations in cache sidechannels, are ineffective against this type of attack due to leaving footprints of execution. Addressing ciphertext side channels necessitates a more holistic approach that combines constant-time coding practices with the attack mechanism. For example, CIPHERFIX [135] employed dynamic taint analysis to identify the offsets of sensitive memory store instructions in a program. Using static instrumentation, it transformed each tainted memory store instruction into a copy that incorporated masking operations in the instrumentation section. A direct jump instruction was then inserted at the original program point, redirecting execution to the newly created copy. However, CIPHERFIX mitigated ciphertext side-channel leakage at the cost of significant performance overhead, ranging from  $2.4 \times$  to  $16.8 \times$ in its most efficient variant, due to the use of static binary instrumentation.

Simultaneously, while efforts are being made to develop new cache designs aimed at countering cache side-channels, a notable challenge arises from the lack of formal guarantees regarding their effectiveness. Novel cache designs that focus on mitigating side channels often introduce complex hardware operations, for example, the randomization process [67, 78–80]. This intricacy makes it difficult to provide rigorous mathematical or formal proofs of their effectiveness. Moreover, the ever-evolving landscape of side-channel attacks means that new vulnerabilities may emerge over time, challenging the robustness of these designs. Thus, despite the innovative solutions being proposed [136–140], the absence of formal guarantees underscores the need for continuous evaluation, and adaptability to ensure that these cache designs effectively thwart emerging side-channel threats in a real-world context.

The challenges and limitations in defending against side-channel attacks discussed earlier provide the foundational motivation for this thesis. The primary objectives of this thesis are threefold:

- Advancing the field of cache side-channel detection by developing more robust and comprehensive methods for identifying and fixing these vulnerabilities.

- Addressing the emerging issue related to the constant-time principle by mitigating ciphertext side channels, which present new and formidable threats in the realm of TEEs.

- Enhancing the security of new cache designs by providing a reasoning framework for formally verifying their effectiveness in countering cache side-channel attacks.

By addressing these critical areas, this thesis seeks to contribute to the ongoing efforts to strengthen the security of modern computing systems in the face of evolving and increasingly sophisticated side-channel threats.

### 1.4 Major Contributions

This thesis makes the following three contributions.

First, we propose CATYPE, a novel refinement type-based tool for detecting cache side channels in cryptography software. Compared to previous works, CATYPE provides the following advantages: For the first time CATYPE analyzes cache side channels using refinement type over x86 assembly code. It reveals several significant and effective enhancements with refined types, including bit-level granularity tracking, distinguishing different effects of variables, precise type inferences, and high scalability. CATYPE is the first static analyzer for cryptography libraries in consideration of blinding-based defenses. From the perspective of implementation, CATYPE uses cache layouts of potentially vulnerable control-flow branches rather than cache states to suppress false positives. We evaluate CATYPE in identifying side-channel vulnerabilities in real-world cryptography software, including RSA, El-Gamal, and (EC)DSA from OpenSSL and Libgcrypt. CATYPE captures all known defects in our dataset (Section 2.6.3), detects previously unknown vulnerabilities

(Section 2.6.4), and reveals several false positives of previous tools (Section 2.6.6). In terms of performance, CATYPE is  $16 \times$  faster than CacheD [133] and  $131 \times$  faster than CacheS [134] when analyzing the same libraries. These evaluation results confirm the capability of CATYPE in identifying side channel defects with great precision, efficiency, and scalability.

Second, we design CIPHERGUARD, a compiler-aided mitigation methodology to counteract ciphertext side channels with high efficiency and security. For the first time, we introduce a compiler-aided strategy to address ciphertext side channels. Through the exploration and implementation of multiple mitigation variants, e.g., software-based probabilistic encryption and secret-aware register allocation, our compiler-aided strategy has been demonstrated to provide a more efficient and flexible solution in comparison to the instrumentation strategy in CIPHER-FIX [135]. CIPHERGUARD is an LLVM-based compiler-aided tool that harnesses dynamic taint analysis and deploys vulnerability mitigation variants at the compilation stage. CIPHERGUARD excels in generating more efficient mitigated code through in-place mitigation code insertion, precise buffer management for random nonces, and flexible register allocation. CIPHERGUARD is evaluated in mitigating ciphertext side-channel vulnerabilities among real-world cryptography software by hardening all the sensitive memory access instructions. With efficient management of random nonce buffers and flexible register allocation, CIPHERGUARD demonstrates a satisfactory performance overhead, averaging  $1.76-3.10 \times$  across various evaluations of cryptography software. This is a significant performance improvement over CIPHERFIX, highlighting the efficacy of the compiler-aided strategy in enhancing the security against ciphertext side channels.

Third, we propose a comprehensive methodology based on formal methods for security verification of cache architectures. Specifically, we design an entropy-based noninterference reasoning framework with two unwinding conditions to assess the information leakage of the cache designs. The reasoning framework quantifies the dependency relationships by the mutual information between the distributions of input and output of side channels. Given a cache design, we formalize its behavior specification along with the cache layouts into an abstract state machine, to instantiate the parameterized reasoning framework that discloses any potential vulnerabilities. We use our methodology to assess eight state-of-the-art cache architectures to demonstrate reliability as well as flexibility.

### 1.5 Outline of the Thesis

The thesis is organized as follows.

Chapter 1 briefly introduces the background of side-channel attacks in various contexts and existing methods for their detection and mitigation. The chapter then defines the scope of the research, delineating the specific areas of focus, such as side-channel detection and mitigation, as well as the verification of novel cache architectures. It also outlines the primary contributions of the research and offers an overview of the thesis's structure.

Chapter 2 reveals the limitations of current cache side-channel detection, providing the motivation of CATYPE's methodology. It discusses CATYPE's innovative features, specifically the refinement type system, and its comprehensive and scalable side-channel vulnerability detection to cryptography libraries. The evaluation results demonstrate CATYPE's precision and efficiency in identifying side-channel vulnerabilities, concluding with a summary of its contributions.

Chapter 3 starts by introducing the emerging threat of ciphertext side channels and CIPHERGUARD's purpose. It explains CIPHERGUARD's automatic recognition of secret-dependent store instructions and multiple precise mitigation variants embedded in the LLVM ecosystem, emphasizing compatibility with TEEs. Evaluation results underline CIPHERGUARD's efficiency and security compared to prior methods, ending with a summary of contributions.

Chapter 4 begins with the importance of formal methods for cache architecture security verification and provides background on the methodology. It details the methodology's application to assess cache architectures, highlighting reliability and flexibility. The chapter concludes with a summary of its contributions and the significance of using formal methods for security verification.

Chapter 5 summarizes the thesis, highlighting contributions like novel cache sidechannel detection tools, while also outlining future research directions, such as quantification of cache side-channel leakage.

## Chapter 2

# Refinement type-based Detection of Side-channels in Cryptography Software

### 2.1 Introduction

Cache-based side channels have demonstrated serious threats to cryptography algorithms, such as the symmetric cipher AES [5, 7], the asymmetric cipher RSA [11, 13, 141], and the digital signature (EC)DSA [142–144]. The essence of these cache attacks is the interference of program memory accesses toward cache units, where secret-dependent memory accesses or program branches leave distinguishable footprints in cache units. Thus, identifying and removing cache interference can eliminate side-channel leakage.